# EXC-2000PCI & EXC-2000PCI e

Test and Simulation Carrier Board for PCI Systems

User's Manual

Copyright © 2009–2023 Excalibur Systems. All Rights Reserved.

# **Table of Contents**

| 1 Intro | oduct                  | ion                                                   |       |

|---------|------------------------|-------------------------------------------------------|-------|

|         | <b>1.1</b> 1.1.1 1.1.2 | Overview                                              | . 1-2 |

|         | 1.1                    | Installation                                          | . 1-4 |

|         |                        | Technical Support                                     |       |

| 2 PCI   |                        | itecture                                              |       |

|         |                        |                                                       | 2 2   |

|         |                        | Memory Structure                                      |       |

|         |                        | PCI Configuration Space Header                        |       |

|         | <b>2.3</b> 2.3.1       | PCI Configuration Registers                           |       |

|         | 2.3.1                  | Device Identification Register (VID)                  |       |

|         | 2.3.3                  | PCI Command Register (PCICMD)                         |       |

|         | 2.3.4                  | PCI Status Register (PCISTS).                         |       |

|         | 2.3.5                  | Revision Identification Register (RID)                |       |

|         | 2.3.6                  | Class Code Register (CLCD)                            |       |

|         | 2.3.7                  | Cache Line Register Size Register (CALN)              |       |

|         | 2.3.8                  | Latency Timer Register (LAT)                          |       |

|         | 2.3.9                  | Header Type Register (HDR)                            |       |

|         | 2.3.10                 | 3 ( )                                                 |       |

|         | 2.3.11                 | Base Address Registers (BADR).                        |       |

|         | 2.3.12                 |                                                       |       |

|         | 2.3.13                 | ,                                                     |       |

|         | 2.3.14                 |                                                       |       |

|         | 2.3.15<br>2.3.16       |                                                       |       |

|         | 2.3.10                 |                                                       |       |

|         | 2.3.17                 |                                                       |       |

|         | 2.3.10                 | . ,                                                   |       |

|         | 2.3.20                 |                                                       |       |

|         |                        | Global and DMA Registers Memory Space Map             |       |

|         |                        |                                                       |       |

|         |                        | Global Registers Map                                  |       |

|         | 2.5.1                  | Board Identification Register                         |       |

|         | 2.5.2                  | Software Reset Register                               |       |

|         | 2.5.3                  | Interrupt Status Register                             |       |

|         | 2.5.4<br>2.5.5         | Interrupt Reset Register                              |       |

|         | 2.5.6                  | Byte Swapping                                         |       |

|         | 2.5.7                  | FPGA Revision Register                                |       |

|         | 2.5.8                  | 2000PCI Family Identifier Register                    |       |

|         | 2.5.9                  | Board Type Register                                   |       |

|         | 2.6                    | Global Timer Registers                                |       |

|         | 2.6.1                  | Timer Prescale Register                               |       |

|         | 2.6.2                  | Timer Preload Register                                |       |

|         | 2.6.3                  | Timer Control Register.                               |       |

|         | 2.6.4                  | General Purpose Timer Register                        |       |

|         |                        | DMA Registers for PCI Express                         |       |

|         | 2.7.1                  | DMA0 Address of Contiguous Host Memory (Low and High) |       |

|         | 2.7.1                  | DMA0 Data Transfer Size                               |       |

|         | 2.7.2                  | DMA0 Control Register                                 |       |

|         |                        |                                                       |       |

| 2.7.4      | DMA1 Address of Contiguous Host Memory                       | 2-19 |

|------------|--------------------------------------------------------------|------|

| 2.7.5      | DMA1 Data Transfer Size                                      | 2-20 |

| 2.7.6      | DMA1 Control Register                                        | 2-20 |

| 2.7.7      | DMA Interrupt Status Register                                | 2-21 |

| 2.7.8      | Base Address for DMA0 and DMA1 Transfers                     | 2-21 |

| 2.7.9      | Repeat Code Register                                         | 2-21 |

| 2.8        | Module Memory Space Map                                      | 2-22 |

| 3 Mechani  | cal and Electrical Specifications                            |      |

| 3.1        | Board Layout                                                 | 3-2  |

| 3.2        | LED Indicators                                               | 3-3  |

| 3.3        | DIP Switches                                                 | 3-3  |

| 3.3.1      | Selected ID DIP Switch [SW1] for Multiple Board Applications |      |

| 3.4        | Connectors                                                   | 3-4  |

| 3.4.1      | EXC-2000PCI Connectors                                       | 3-4  |

| 3.4.2      | EXC-2000PCle Connectors                                      | 3-4  |

| 3.4.3      | Communications I/O Connector [J1] and [J2]                   | 3-5  |

| 3.4.4      |                                                              |      |

| 3.4.5      | . c. =/p                                                     |      |

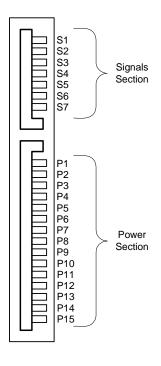

| 3.4.6      | SATA Connector for PCI Express for Power Only [J3]           | 3-15 |

| 3.5        | Power Requirements                                           | 3-16 |

| 4 Ordering | g Information                                                |      |

# **Figures**

| Figure 1-1 | EXC-2000PC/ Block Diagram                                  | 1 <b>-</b> 3 |

|------------|------------------------------------------------------------|--------------|

| Figure 1-2 | EXC-2000PCIe Block Diagram                                 | 1-3          |

| Figure 2-1 | PCI Configuration Space Header                             | 2-3          |

| Figure 2-2 | PCI Express Configuration Space Header                     | 2-4          |

| Figure 2-3 | Global and DMA Registers Memory Space Map                  | 2-11         |

| Figure 2-4 | EXC-2000PCI[e] Global Registers Map                        | 2-12         |

| Figure 2-5 | Module Memory Space Map                                    | 2-22         |

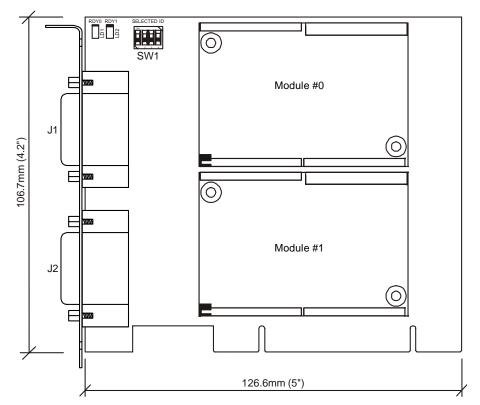

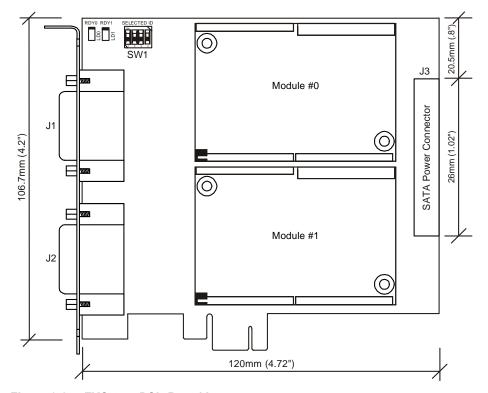

| Figure 3-1 | EXC-2000PCI Board Layout                                   | 3-2          |

| Figure 3-2 | EXC-2000PCle Board Layout                                  | 3-2          |

| Figure 3-3 | DIP Switch SW1 with All Contacts Set to ON (Selected ID#0) | 3-3          |

| Figure 3-4 | High-density HDB-26 Pin Female Connector – Front View      | 3-5          |

| Figure 3-5 | 15+7-Pin Male SATA Connector [J3] – Front View             | 3-15         |

|            |                                                            |              |

# **Tables**

| Table 2-1  | PCI Command Register                              | 2-5  |

|------------|---------------------------------------------------|------|

| Table 2-2  | PCI Status Register for PCI Boards                | 2-6  |

| Table 2-3  | PCI Status Register for PCIe Boards               | 2-7  |

| Table 2-4  | Base Address Registers Definition for PCI Boards  | 2-9  |

| Table 2-5  | Base Address Registers Definition for PCIe Boards |      |

| Table 2-6  | Base Address Register for PCI Boards              | 2-9  |

| Table 2-7  | Base Address Register for PCIe Boards             | 2-10 |

| Table 2-8  | Board Identification Register                     | 2-13 |

| Table 2-9  | Software Reset Register                           | 2-13 |

| Table 2-10 | Interrupt Status Register                         | 2-13 |

| Table 2-11 | Interrupt Reset Register                          | 2-14 |

| Table 2-12 | Module Info Registers                             | 2-14 |

| Table 2-13 | Byte Swapping Register                            | 2-15 |

| Table 2-14 | Timer Prescale/General Purpose Timer Resolution   | 2-16 |

| Table 2-15 | Timer Control Register                            | 2-17 |

| Table 2-16 | DMA0 Control Register                             | 2-19 |

| Table 2-17 | DMA1 Control Register                             | 2-20 |

| Table 2-18 | Repeat Code Register                              | 2-21 |

| Table 3-1  | LED Indicators                                    | 3-3  |

| Table 3-2  | Selected ID Values                                |      |

| Table 3-3  | J1/J2 Connector Pinouts for M4K429RTx Modules     | 3-6  |

| Table 3-4  | J1/J2 Connector Pinouts for M4K708 Modules        | 3-7  |

| Table 3-5  | J1/J2 Connector Pinouts for M4K717 Modules        | 3-8  |

| Table 3-6  | J1/J2 Connector Pinouts for M4KSerialPlus Modules | 3-9  |

| Table 3-7  | J1/J2 Connector Pinouts for M4KDiscrete Modules   | 3-10 |

| Table 3-8  | J1/J2 Connector Pinouts for M4KCAN Modules        | 3-11 |

| Table 3-9  | J1/J2 Connector Pinouts for M4K825CAN Modules     | 3-12 |

| Table 3-10 | PCI Bus Edge Connector Pinout                     | 3-13 |

| Table 3-11 | PCI Express Bus Edge Connector Pinout             | 3-14 |

| Table 3-12 | 15+7-Pin Male SATA Connector Pinouts [J3]         | 3-15 |

| Table 4-1  | Ordering Information                              | 4-1  |

| Table 4-2  | M4K Module Codes and Part Numbers                 | 4-1  |

page iv Excalibur Systems

## 1 Introduction

| 1.1 | Overview            | -1 |

|-----|---------------------|----|

|     | .1.1 Board Features | -2 |

|     | .1.2 Block Diagram  | -3 |

| 1.1 | nstallation1        | -4 |

| 1.1 | Fechnical Support   | _4 |

Note: The *EXC-2000PCle* board will not work without the power cable connected. See 1.1 Installation on page 1-4.

#### 1.1 Overview

The *EXC-2000PCI[e]* is a multiprotocol, PCI interface board for avionics test and simulation applications. Each board can hold up to 2 independent modules from the modules listed below:

| M4K429RT <i>x</i> | ARINC 429 multi-channel interface module. This module supports either five or ten ARINC 429 channels each of which can be configured in real time as a receive or transmit channel.                                                                               |

|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M4K708            | ARINC 708 interface module. This module supports up to two ARINC 708/453 channels for the Weather Radar Display Databus. Each channel is selectable as transmit or receive and implements a 64K-word FIFO and supports polling and/or interrupt driven operation. |

| M4K717            | ARINC 717 interface module. This module supports two ARINC 717 receive channels and two transmit channels.                                                                                                                                                        |

| M4KSerialPlus     | Serial communications interface module. This module supports either two or four independent channels of serial communications, each of which can be selected as RS485, RS422 or RS232.                                                                            |

| M4KDiscrete       | Discrete I/O interface module. This module supports 20 bi-directional Discretes with TTL (0 to 5 volts) or avionics (0 to 32 volts) voltage levels.                                                                                                               |

| M4KCAN            | CAN protocol interface module. This module supports either two, four or six independent channels of CAN 2.0B protocol with standard and extended message frames and message identifiers.                                                                          |

| M4K825CAN         | ARINC 825 interface module. The module supports up to ten ARINC 825 channels.                                                                                                                                                                                     |

In addition Excalibur produces MIL-STD-1553, MMSI and H009 protocol modules for use with its *EXC-4000* family of carrier boards. More information about these and other Excalibur products is available on our website: <a href="https://www.mil-1553.com">www.mil-1553.com</a>

All modules come with Windows drivers, including source code, mating connectors and plastic hoods.

#### 1.1.1 Board Features

#### **General Specifications**

EXC-2000PCI[e] Smaller than Half-size PCI or PCI Express Board (see Dimensions)

Supports up to 2 modules

Protocols supported: ARINC-429/575 (5 or 10 channels per module)

ARINC 708/453 (2 ch. per module) ARINC 717 (2 ch. per module) Discrete I/O (20 ch. per module)

Serial - RS485/RS422/RS232 (2 or 4 ch. per module)

CAN (2, 4, or 6 ch. per module)

ARINC 825 (CAN) (2, 4, 6 or 10 ch. per module)

**Operating Environment**

Temperature: 0° to 70°C standard temp.

-40° to +85°C extended temp. (optional)

Humidity: 5% – 90% non-condensing

**Physical Characteristics**

PCI Board PCIe Board

Dimension 126.6mm (5") x 106.7mm (4.2") 120mm (4.72") x 106.7mm (4.2")

Weight 102g\* 103g\*

\* without modules

**Host Interface**

PCI compliance: Master/Target 8/16 bit

PCI Express compliance: x1 lane PCle v1.1 with incorporated DMA data transfer

Memory space occupied: 512 Kbytes Interrupts: INTA#

Power Depends on configuration

MTBF 560,100 hours at 25°C, G<sub>F</sub>, S217F

**Software Support**

C Drivers with source code

Mystic Windows software for 429 modules

For exact part numbers, see Chapter 4 Ordering Information.

#### 1.1.2 Block Diagram

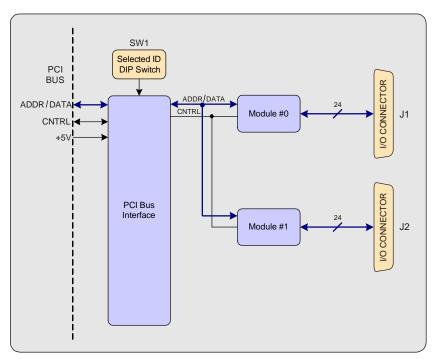

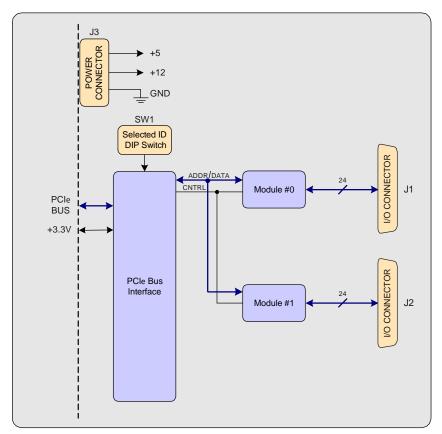

Figure 1-1 EXC-2000PCI Block Diagram

Figure 1-2 EXC-2000PCIe Block Diagram

#### 1.1 Installation

For hardware and software installation instructions, see Installation Instructions.pdf in the root folder of the installation CD. When downloading new software from the Excalibur website, Installation Instructions.pdf is contained in the zip file.

The *Excalibur Installation CD* you received with your package is the most recent release of the CD as of the date of shipping. Software and documentation updates can be found and downloaded from our website: www.mil-1553.com.

The standard software provided with Excalibur boards and modules is for Windows operating systems. For more details, see **Installation Instructions.pdf**. Software for other operating systems may be available. Check on our website or write to excalibur@mil-1553.com.

## 1.1 Technical Support

Excalibur Systems is ready to assist you with any technical questions you may have. For technical support, visit the <u>Technical Support</u> page of our website (<u>www.mil-1553.com</u>). You can also contact us by phone. To find the location nearest you, visit to the <u>Contact Us</u> page of our website. Before contacting Technical Support, please see <u>Information Required for Technical Support</u>.

page 1 - 4 Excalibur Systems

# 2 PCI Architecture

Chapter 2 describes the PCI architecture. The following topics are covered:

| 2.1 | Memoi          | ry Structure                                          | 2-2  |

|-----|----------------|-------------------------------------------------------|------|

| 2.2 | PCI Co         | onfiguration Space Header                             | 2-3  |

| 2.3 |                | onfiguration Registers                                |      |

|     | 2.3.1          | Vendor Identification Register (VID)                  |      |

|     | 2.3.2          | Device Identification Register (DID)                  |      |

|     | 2.3.3          | PCI Command Register (PCICMD)                         |      |

|     | 2.3.4          | PCI Status Register (PCISTS)                          |      |

|     | 2.3.5          | Revision Identification Register (RID)                |      |

|     | 2.3.6          | Class Code Register (CLCD)                            |      |

|     | 2.3.7          | Cache Line Register Size Register (CALN)              | 2-8  |

|     | 2.3.8          | Latency Timer Register (LAT)                          |      |

|     | 2.3.9          | Header Type Register (HDR)                            |      |

|     | 2.3.10         |                                                       |      |

|     | 2.3.11         | Base Address Registers (BADR)                         |      |

|     | 2.3.12         |                                                       |      |

|     | 2.3.13         | Subsystem ID                                          |      |

|     | 2.3.14         | Subvendor ID                                          |      |

|     | 2.3.15         | Expansion ROM Base Address Register (XROM)            |      |

|     | 2.3.16         | PCI Capabilities Pointer                              |      |

|     | 2.3.17         | Interrupt Line Register (INTLN)                       |      |

|     | 2.3.18         | Interrupt Pin Register (INTPIN)                       |      |

|     | 2.3.19         | Minimum Grant Register (MINGNT)                       |      |

|     | 2.3.20         | Maximum Latency Register (MAXLAT)                     |      |

| 2.4 |                | I and DMA Registers Memory Space Map                  |      |

| 2.5 |                | Registers Map                                         |      |

| 2.5 | 2.5.1          |                                                       |      |

|     | 2.5.1          | Board Identification Register                         |      |

|     | 2.5.2          | Interrupt Status Register                             |      |

|     | 2.5.4          | Interrupt Reset Register                              |      |

|     | 2.5.5          | Module Info Registers                                 |      |

|     | 2.5.6          | Byte Swapping                                         |      |

|     | 2.5.7          | FPGA Revision Register                                |      |

|     | 2.5.8          | 2000PCI Family Identifier Register                    |      |

|     | 2.5.9          | Board Type Register                                   |      |

| 2.6 |                | I Timer Registers                                     |      |

| 2.0 | 2.6.1          | Timer Registers                                       |      |

|     | 2.6.2          | Timer Preload Register                                |      |

|     | 2.6.3          | Timer Control Register                                |      |

|     | 2.6.4          | General Purpose Timer Register                        |      |

| 27  |                | Registers for PCI Express                             |      |

| 2.1 |                | •                                                     |      |

|     | 2.7.1          | DMA0 Address of Contiguous Host Memory (Low and High) |      |

|     | 2.7.2          | DMA0 Octobrol Borriston                               |      |

|     | 2.7.3          | DMA0 Control Register                                 |      |

|     | 2.7.4          | DMA1 Address of Contiguous Host Memory                |      |

|     | 2.7.5<br>2.7.6 | DMA1 Control Register                                 |      |

|     | 2.7.6<br>2.7.7 | DMA1 Control Register                                 |      |

|     | 2.7.8          | DMA Interrupt Status Register                         |      |

|     | 2.7.0          | Repeat Code Register                                  |      |

| 2.0 |                | •                                                     |      |

| 2.8 | would          | e Memory Space Map                                    | 2-22 |

## 2.1 Memory Structure

The EXC-2000PCI requests two memory blocks:

• The first memory block (Base 0) is 512 KB in size and contains the memory space for the modules on the board. For more information, see 2.8 Module Memory Space Map on page 2-22.

• The second memory block (Base 1) is 64 bytes in size and contains the Global Registers. For more information, see 2.5 Global Registers Map on page 2-12.

The EXC-2000PCIe requests two memory blocks:

- The first memory block (Base 0) is 512 KB in size and contains the memory space for the modules on the board. For more information, see **2.8 Module Memory Space Map** on page 2-22.

- The second memory block (Base 2) is 16 KB in size and contains the Global and DMA registers. For more information, see 2.5 Global Registers Map on page 2-12 and 2.7 DMA Registers for PCI Express on page 2-18.

page 2 - 2 Excalibur Systems

## 2.2 PCI Configuration Space Header

The board includes a PCI Configuration Space Header, as required by the PCI specification. The registers contained in this header enable software to set up the Plug and Play operation of the board, and set aside system resources.

The following figures show the PCI and PCIe Configuration Space Header:

| MAX_LAT                                      | MIN_GNT             | Interrupt Pin        | Interrupt Line  | 3C H |

|----------------------------------------------|---------------------|----------------------|-----------------|------|

|                                              | Reserv              | ed = 0s              |                 | 38 H |

|                                              | Reserved = 0s       |                      | Cap. pointer    | 34 H |

|                                              | Expansion ROM Bas   | e Address (not used) |                 | 30 H |

| Subsys                                       | stem ID             | Subsystem            | vendor ID       | 2C H |

|                                              | Cardbus CIS Po      | ointer (not used)    |                 | 28 H |

|                                              | Base Address Reg    | gister #5 (not used) |                 | 24 H |

|                                              | Base Address Reg    | gister #4 (not used) |                 | 20 H |

| Base Address Register #3 (not used)          |                     |                      |                 | 1C H |

| Base Address Register #2 (not used)          |                     |                      |                 | 18 H |

| Base Address Register #1 – Global Registers  |                     |                      |                 | 14 H |

| Base Address Register #0 Module Memory Space |                     |                      |                 | 10 H |

| BIST                                         | Header Type = 0     | Latency Timer        | Cache Line Size | 0C H |

| Class Code Rev ID                            |                     |                      |                 | 08 H |

| Status Register Command Register             |                     |                      |                 | 04 H |

| Devi                                         | Device ID Vendor ID |                      |                 |      |

| 31 24                                        | 23 16               | 15 08                | 07 00           |      |

Figure 2-1 PCI Configuration Space Header

| MAX                                                 | _LAT                                           | MIN_GNT          | Interrupt Pin         | Interrupt Line  | 3C H |

|-----------------------------------------------------|------------------------------------------------|------------------|-----------------------|-----------------|------|

|                                                     | Reserved = 0s                                  |                  |                       |                 | 38 H |

|                                                     |                                                | Reserved = 0s    |                       | Cap. pointer    | 34 H |

|                                                     |                                                | Expansion ROM Ba | se Address (not used) |                 | 30 H |

|                                                     | Subsys                                         | stem ID          | Subsystem             | n Vendor ID     | 2C H |

|                                                     |                                                | Cardbus CIS F    | ointer (not used)     |                 | 28 H |

|                                                     |                                                | Base Address Re  | gister #5 (not used)  |                 | 24 H |

|                                                     |                                                | Base Address Re  | gister #4 (not used)  |                 | 20 H |

| Base Address Register #3 (not used)                 |                                                |                  |                       |                 | 1C H |

| Base Address Register #2 – Global and DMA Registers |                                                |                  |                       | gisters         | 18 H |

|                                                     | Base Address Register #1 (not used)            |                  |                       |                 | 14 H |

|                                                     | Base Address Register #0 – Module Memory Space |                  |                       | 10 H            |      |

| BIS                                                 | ST                                             | Header Type = 0  | Latency Timer         | Cache Line Size | 0C H |

|                                                     |                                                | Class Code       |                       | Rev ID          | 08 H |

|                                                     | Status I                                       | Register         | Comman                | d Register      | 04 H |

|                                                     | Devi                                           | ce ID            | Vend                  | lor ID          | 00 H |

| 31                                                  | 24                                             | 23 16            | 15 08                 | 07 00           | 1    |

Figure 2-2 PCI Express Configuration Space Header

page 2 - 4 Excalibur Systems

## 2.3 PCI Configuration Registers

#### 2.3.1 Vendor Identification Register (VID)

Power-up value 1405 H

Size: 16 bits

The Vendor Identification register contains the PCI Special Interest Group vendor identification number assigned to Excalibur Systems.

Address:

Address:

Address:

00-01 (H)

02-03 (H)

04-05 (H)

#### 2.3.2 Device Identification Register (DID)

Power-up value: PCI Board: 4006 H

PCle Board: E406 H

Size: 16 bits

The Device Identification register contains the board's device identification number.

#### 2.3.3 PCI Command Register (PCICMD)

Power-up value: 0000 H Size: 16 bits

The PCI Command register contains the PCI Command.

| Bit   | Bit Name                              | Description                                                                    |

|-------|---------------------------------------|--------------------------------------------------------------------------------|

| 10-15 | Reserved                              | Set to 0s                                                                      |

| 09    | Fast Back-to Back<br>Enable           | Always set to 0                                                                |

| 08    | System Error Enable                   | Always set to 0                                                                |

| 07    | Address Stepping<br>Support           | PCI Board: Always set to 1 PCIe Board: Always set to 0                         |

| 06    | Parity Error Enable                   | Always set to 0                                                                |

| 05    | VGA Palette Snoop<br>Enable           | Always set to 0                                                                |

| 04    | Memory Write and<br>Invalidate Enable | Always set to 0                                                                |

| 03    | Special Cycle Enable                  | Always set to 0                                                                |

| 02    | Bus Master Enable                     | PCI Board: Always set to 0 PCIe Board: Always set to 1                         |

| 01    | Memory Access Enable                  | Always set to 1                                                                |

| 00    | I/O Access Enable                     | Since the board does not use I/O space, the value of this register is ignored. |

Table 2-1 PCI Command Register

06-07 (H)

Address:

## 2.3.4 PCI Status Register (PCISTS)

Power-up value: 0080 H Size: 16 bits

The PCI Status register contains the PCI status information.

| Bit   | Bit Name                                    | Description                                                                                                                                                                        |

|-------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | Detected Parity<br>Error                    | This bit is set whenever a parity error is detected. It functions independently from the state of Command Register Bit 6. This bit may be cleared by writing a 1 to this location. |

| 14    | Signaled System<br>Error                    | Not used                                                                                                                                                                           |

| 13    | Received Master<br>Abort                    | Not used                                                                                                                                                                           |

| 12    | Received Target<br>Abort                    | Not used                                                                                                                                                                           |

| 11    | Signaled Target<br>Abort                    | This bit is set whenever this device aborts a cycle when addressed as a target. This bit can be reset by writing a 1 to this location.                                             |

| 09-10 | Device Select<br>(DEVSEL#)<br>Timing Status | Set to 10 (slow timing)                                                                                                                                                            |

| 08    | Data Parity<br>Reported                     | Not used                                                                                                                                                                           |

| 07    | Fast Back-to-<br>Back Capable               | Set to 1                                                                                                                                                                           |

| 06    | Reserved                                    |                                                                                                                                                                                    |

| 05    | 66MHz capable                               | Set to 0                                                                                                                                                                           |

| 04    | Capability List enable                      | Set to 1                                                                                                                                                                           |

| 00-03 | Reserved                                    |                                                                                                                                                                                    |

Table 2-2 PCI Status Register for PCI Boards

page 2 - 6 Excalibur Systems

| Bit   | Bit Name                                    | Description                                                                                                                                                                        |

|-------|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15    | Detected Parity<br>Error                    | This bit is set whenever a parity error is detected. It functions independently from the state of Command Register Bit 6. This bit may be cleared by writing a 1 to this location. |

| 14    | Signaled System<br>Error                    | Not used                                                                                                                                                                           |

| 13    | Received Master<br>Abort                    | This bit is set when the device receives a master abort to terminate a transaction. This bit can be reset by writing a 1 to this location.                                         |

| 12    | Received Target<br>Abort                    | Not used                                                                                                                                                                           |

| 11    | Signaled Target<br>Abort                    | Not used                                                                                                                                                                           |

| 09-10 | Device Select<br>(DEVSEL#)<br>Timing Status | Set to 00 (fast timing)                                                                                                                                                            |

| 08    | Data Parity<br>Reported                     | Not used                                                                                                                                                                           |

| 07    | Fast Back-to-<br>Back Capable               | Set to 0                                                                                                                                                                           |

| 06    | <b>UDF Supported</b>                        | Set to 0                                                                                                                                                                           |

| 05    | 66MHz capable                               | Set to 0                                                                                                                                                                           |

| 04    | Capability List enable                      | Set to 1                                                                                                                                                                           |

| 03    | Interrupt Status                            | This bit is set when an interrupt is received.                                                                                                                                     |

| 00-02 | Reserved                                    |                                                                                                                                                                                    |

Table 2-3 PCI Status Register for PCIe Boards

#### 2.3.5 Revision Identification Register (RID)

Power-up value: 01 H

Size: 8 bits

The Revision Identification register contains the revision identification number of the board.

#### 2.3.6 Class Code Register (CLCD)

Power-up value: FF0000 H Size: 24 bits

The Class code Register value indicates that the board does not fit into any of the defined class codes.

Address:

Address:

08 (H)

09--0B (H)

2.3.7 Cache Line Register Size Register (CALN)

Address: 0C (H)

Power-up value: PCI Board: 00 H

PCle Board: 10 H

Size: 8 bits

Not used

2.3.8 Latency Timer Register (LAT)

Address: 0D (H)

Power-up value: 00 H

Size: 8 bits

Not used

2.3.9 Header Type Register (HDR)

Address: 0E (H)

Power-up value: 00 H

Size: 8 bits

The board is a single function PCI device.

Address: 0F (H)

Power-up value: 00 H

Size: 8 bits

**Built-In Self-Test Register (BIST)**

The Built-In Self-Test register is not implemented in the board.

2.3.10

#### 2.3.11 Base Address Registers (BADR)

Address: 10, 14, 18, 1C,

20, 24 (H)

Power-up value: 000000000 H for each

Size: 32 bits

The Base Address Registers are used by the system BIOS to determine the number, size and base addresses of memory pages required by the board, within host address space.

**For PCI Boards:** Two memory pages are required by the board: one for the Module Memory Space and one for the Global Registers.

| Register       | Offset | Size       | Function               |

|----------------|--------|------------|------------------------|

| Base Address 0 | 10 H   | 512 K Byte | Module Memory<br>Space |

| Base Address 1 | 14 H   | 64 Byte    | Global registers       |

Table 2-4 Base Address Registers Definition for PCI Boards

**For PCle Boards:** Two memory pages are required by the board: one for the Module Memory Space, one for the Global Registers and DMA Registers.

| Register       | Offset | Size   | Function                 |

|----------------|--------|--------|--------------------------|

| Base Address 0 | 10 H   | 512 KB | Module Memory<br>Space   |

| Base Address 2 | 18 H   | 16 KB  | Global and DMA registers |

Table 2-5 Base Address Registers Definition for PCle Boards

**Note:** Each Base Address Register contains 32 bits. Since the PCI Express board uses 64-bit address space, each memory page covers two base addresses (0-1, 2-3, 4-5).

The following table describes the bits of the Base Address Register.

| Bit   | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 04-31 | Address of memory region (with lower 4 bits removed)                    |

| 03    | Always 0 – memory is not prefetchable                                   |

| 01-02 | Always 0 – memory may be mapped anywhere within the 32 bit memory space |

| 00    | Always 0 – indicates memory space                                       |

Table 2-6 Base Address Register for PCI Boards

| Bit   | Description                                                             |

|-------|-------------------------------------------------------------------------|

| 04-31 | Address of memory region (with lower 4 bits removed)                    |

| 03    | Always 1 – memory is prefetchable                                       |

| 01-02 | Always 2 – memory may be mapped anywhere within the 64 bit memory space |

| 00    | Always 0 – indicates memory space                                       |

Table 2-7 Base Address Register for PCle Boards

#### 2.3.12 Cardbus CIS Pointer

Address: 28 (H)

Power-up value:

00000000 H

Size:

32 bits

The Cardbus Pointer is not implemented on the board.

#### 2.3.13 Subsystem ID Address: 2C (H)

Power-up value: 0000 H Size: 16 bits

#### 2.3.14 Subvendor ID Address: 2E (H)

Power-up value: 0000 H Size: 16 bits

#### 2.3.15 Expansion ROM Base Address Register (XROM) Address: 30 (H)

Power-up value:

00000000 H

Size:

32 bits

The Expansion ROM Space is not implemented on the board.

#### 2.3.16 PCI Capabilities Pointer Address: 34 (H)

Power-up value: 50 H

Size: 8 bits

The PCI Capabilities Pointer (Cap. Pointer) indicates the location of the PCI Capabilities Identification (ID) Register. The Capabilities ID Register stores a pointer to a structure within the configuration space. With a known Capabilities ID value, the associated structure can be found during the scanning process.

#### 2.3.17 Interrupt Line Register (INTLN)

Power-up value: 00 H

Size: 8 bits

The Interrupt Line register indicates the interrupt routing for the PCI Controller. The value of this register is system-architecture specific. For x86-based PCs, the values in this register correspond with the established interrupt numbers associated with the dual 8259 controllers used in those machines; the values of 1 to F (H) correspond with the IRQ numbers 1 through 15, and the values from 10(H) to FE (H) are reserved. The value of 255 signifies either "unknown" or "no connection" for the system interrupt.

#### 2.3.18 Interrupt Pin Register (INTPIN)

Power-up value: 01 H

Size: 8 bits

Set to INTA#

#### 2.3.19 Minimum Grant Register (MINGNT)

Power-up value: 00 H

Size: 8 bits

The Minimum Grant register is not implemented on the board.

#### 2.3.20 Maximum Latency Register (MAXLAT)

Power-up value: 00 H

Size: 8 bits

The Maximum Latency register is not implemented on the board.

## 2.4 Global and DMA Registers Memory Space Map

The Global and DMA Registers are mapped as follows.

| Reserved         | 3FFF H |

|------------------|--------|

| Reserved         | 2000 H |

| DMA Registers    | 1FFF H |

|                  | 1000 H |

| Global Registers | 0FFF H |

| Global Registers | 0000 H |

Figure 2-3 Global and DMA Registers Memory Space Map

3C (H)

3D (H)

3E (H)

3F (H)

Address:

Address:

Address:

Address:

# 2.5 Global Registers Map

The global registers reside in the second memory block.

| Reserved                  | 34 – 0FFF H |

|---------------------------|-------------|

| Board Type                | 32 H        |

| 2000PCI Family Identifier | 30 H        |

| Reserved                  | 2A – 2E H   |

| General Purpose Timer     | 28 H        |

| Timer Control             | 26 H        |

| Timer Preload             | 24 H        |

| Timer Prescale            | 22 H        |

| FPGA Revision             | 20 H        |

| Reserved                  | 14 – 1E H   |

| Byte Swapping             | 12 H        |

| Reserved                  | 0C – 10 H   |

| Module 1 Info             | 0A H        |

| Module 0 Info             | 08 H        |

| Interrupt Reset           | 06 H        |

| Interrupt Status          | 04 H        |

| Software Reset            | 02 H        |

| Board ID                  | 00 H        |

Figure 2-4 EXC-2000PCI[e] Global Registers Map

page 2 - 12 Excalibur Systems

#### 2.5.1 Board Identification Register

Address: 00 (H) Length 16 bits

**Read only** The Board Identification register comprises the following identification items.

| Bit   | Description                                                                                     |

|-------|-------------------------------------------------------------------------------------------------|

| 04-15 | PCI Board: Hard coded to the value 400 H PCIe Board: Hard coded to the value 4E0 H              |

| 00-03 | Selected ID See 3.3.1 Selected ID DIP Switch [SW1] for Multiple Board Applications on page 3-3. |

Table 2-8 Board Identification Register

#### 2.5.2 Software Reset Register

Address: 02 (H) Length 16 bits

Write only The Software Reset register performs reset operations of the modules. Individual modules may be reset.

Bit 04, the Global Time Tag reset bit, resets all the module's Time Tag counters.

| Bit   | Description           |                                                  |

|-------|-----------------------|--------------------------------------------------|

| 05-15 | Reserved – set to 0   |                                                  |

| 04    | Global time tag reset | 1 = reset all time tag counters<br>0 = no effect |

| 02-03 | Reserved – set to 0   |                                                  |

| 01    | Module 1 reset        | 1 = reset module<br>0 = no effect                |

| 00    | Module 0 reset        | 1 = reset module<br>0 = no effect                |

Table 2-9 Software Reset Register

#### 2.5.3 Interrupt Status Register

Address: 04 (H) Length 16 bits

**Read only** The Interrupt Status register indicates which modules are currently interrupting or if the General Purpose Timer has produced an interrupt.

| Bit   | Description                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 05-15 | Reserved – set to 0                                                                                                                                |

| 04    | <ul><li>1 = indicates that an interrupt was generated by<br/>the General Purpose Timer [See 2.6 Global<br/>Timer Registers on page 2-16]</li></ul> |

| 02-03 | Reserved – set to 0                                                                                                                                |

| 01    | 1 = indicates that module 1 is interrupting                                                                                                        |

| 00    | 1 = indicates that module 0 is interrupting                                                                                                        |

Table 2-10 Interrupt Status Register

Note: See also 2.7.7 DMA Interrupt Status Register on page 2-21.

#### 2.5.4 Interrupt Reset Register

Address: 06 (H) Length 16 bits

Write only The Interrupt Reset register resets the interrupting modules by writing to the relevant bits of the register.

| Bit   | Description                                                                        |

|-------|------------------------------------------------------------------------------------|

| 05-15 | Reserved – set to 0                                                                |

| 04    | <ul><li>1 = Resets General Purpose Timer interrupt</li><li>0 = No effect</li></ul> |

| 02-03 | Reserved – set to 0                                                                |

| 01    | 1 = Resets module 1 interrupt<br>0 = No effect                                     |

| 00    | 1 = Resets module 0 interrupt<br>0 = No effect                                     |

Table 2-11 Interrupt Reset Register

Note: See also 2.7.7 DMA Interrupt Status Register on page 2-21.

#### 2.5.5 Module Info Registers

Address: 08, 0A (H) Length 16 bits each

**Read only** The Module Info Registers provide identification information for each of the modules.

| Bit   | Description         |                                                                                                                                                                                                                                                                  |

|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-15 | Module ID           | 00 H = Module 0 Info register (at address 08 H)<br>01 H = Module 1 Info register (at address 0A H)                                                                                                                                                               |

| 05-11 | Reserved – set to 0 |                                                                                                                                                                                                                                                                  |

| 00-04 | Module type         | 02 H = M4KSerial 04 H = M4K429RTx module 07 H = M4K708 module 08 H = M4K825CAN module (for EXC-2000PCle only) 12 H = M4KSerialPlus module 17 H = M4K717 module (for EXC-2000PCle only) 0C H = M4KCAN module 0D H = M4KDiscrete module 1F H = no module installed |

Table 2-12 Module Info Registers

page 2 - 14 Excalibur Systems

#### **Byte Swapping** 2.5.6

Address: 12 (H) Length 16 bits

Read/Write The Byte Swapping Register may be used to swap the high byte with the low byte of the Module Memory Space and the Global registers on the board. This may be useful on some host computers that byte-swap their memory.

| Bit   | Description     | _                               |

|-------|-----------------|---------------------------------|

| 00-15 | A1A1            | Enable byte swapping            |

|       | Any other value | Disable byte swapping (Default) |

Table 2-13 Byte Swapping Register

#### 2.5.7 **FPGA Revision Register**

Address: 20 (H) Length 16 bits

The FPGA Revision register contains the FPGA revision of the board. For Read only example, for FPGA revision 1.5, the register would contain the value 0015 (H).

#### 2.5.8 2000PCI Family Identifier Register

Address: 30 (H) Length 16 bits

The 2000PCI Family Identifier register is hard coded to value of 2000 (H). Read only

#### **Board Type Register** 2.5.9

Address: 32 (H) Length 16 bits

Read only The Board Type register comprises the following items.

| Bit   | Description                           |                  |

|-------|---------------------------------------|------------------|

| 00-15 | Hard coded to: PCI Board: PCIe Board: | 4006 H<br>E406 H |

**Board Type Register**

## 2.6 Global Timer Registers

See **2.5 Global Registers Map** on page 2-12 for location of the registers on the memory map.

#### 2.6.1 Timer Prescale Register

Address: 22 (H) Bits 15 – 0

Read/Write The Timer Prescale Register defines the resolution of the General Purpose Timer. It is based on the Global Time Tag Clock (nominally 1 MHz) and thus will give the General Purpose Timer resolution as follows:

| Timer Prescale<br>Register Value (DEC) | General Purpose Time<br>Resolution (μsec) |

|----------------------------------------|-------------------------------------------|

| 0 or 1                                 | 1 (default)                               |

| 2                                      | 2                                         |

| 3                                      | 3                                         |

| •                                      | •                                         |

| •                                      | •                                         |

| •                                      | •                                         |

| 10                                     | 10                                        |

| •                                      | •                                         |

| •                                      | •                                         |

| •                                      | •                                         |

| 65535                                  | 65535                                     |

Table 2-14 Timer Prescale/General Purpose Timer Resolution

**Note:** The Timer Prescale register can only be changed when the timer has been stopped.

#### 2.6.2 Timer Preload Register

Address: 24 (H) Bits 15 – 0

Read/Write The value stored in the Timer Preload Register sets the starting count value for the General Purpose Timer from which it will start to count down. The Timer Preload Register can only be changed while the timer is stopped and has a maximum count value of 65535.

**Note:** The General Purpose Timer will not start counting if a value of zero is stored into the Timer Preload Register.

Default value: 00 00

#### 2.6.3 Timer Control Register

Address: 26 (H) Bits 3 – 0

Read/Write The Timer Control Register is used to control the General Purpose Timer register.

The value stored in bits 01 to 03 take effect when the General Purpose timer reaches a value of zero. Bit 00 is used to start and stop the General Purpose

page 2 - 16 Excalibur Systems

Timer. The values of bits 01 - 03 can only be changed when the General Purpose Timer register is stopped.

Default value: 00 00

| Bit   | Description                     |        |                                                                                         |

|-------|---------------------------------|--------|-----------------------------------------------------------------------------------------|

| 04-15 | Reserved - set to 0             |        |                                                                                         |

| 03    | Global reset on count completed | 1<br>0 | Causes global reset of all installed modules<br>No effect                               |

| 02    | Interrupt on count completed    | 1      | Output an interrupt (see <b>2.5.3 Interrupt Status Register</b> on page 2-13) No effect |

| 01    | Reload mode                     | 1<br>0 | Reload mode<br>Non-reload/One-shot mode                                                 |

| 00    | Start/Stop                      | 1<br>0 | Start<br>Stop                                                                           |

Table 2-15 Timer Control Register

#### 2.6.4 General Purpose Timer Register

Address: 28 (H) Bits 15 – 0

#### Read Only

The General Purpose Timer Register stores the current count value of the General Purpose Timer. The General Purpose Timer is controlled by the Timer Control Register. When the General Purpose Timer is started it will count down to zero, at which point either an interrupt can be generated and or all installed modules can be reset.

If the General Purpose Timer is in reload mode then the current value in Timer Preload Register will be stored into the General Purpose Timer and the timer will start to count down from this value.

If the General Purpose Timer is in non-reload / one shot mode, when it reaches zero it will stop and a value of zero will be displayed in the General Purpose Timer Register. In this case bit 00 (Start/Stop bit) of the Timer Control Register will automatically be set to zero in this case. If the General purpose Timer Register is then started it will start to count from the current Timer Preload Register value automatically (without the need to do a write to the Timer Preload Register).

At any point in time, the General Purpose Timer can be stopped at the current count value. When a start is then issued, the General purpose Timer will start to count down from this current count value. If the user wishes to stop the counter and start from the original preload value or from a new preload value, this value will need to be rewritten into the Timer Preload register prior to the restarting of the General Purpose Timer register.

Note: The maximum clock period of the General Purpose Timer is 4295 seconds (1 hour, 11min & 35 Seconds).

## 2.7 DMA Registers for PCI Express

Direct Memory Access (DMA) enables the board to access a module's memory space for reading and writing independently of the computer's CPU. This results in faster data transfer to and from the board, with much less CPU overhead than when not using DMA.

There are two DMA channels:

- DMAO DMA channel 0 is used for DMA writes

- DMA1 DMA channel 1 is used for DMA reads

| Reserved                                              | 1048 – 1FFF (H) |

|-------------------------------------------------------|-----------------|

| Repeat Code Register                                  | 1044 H          |

| Base Address for DMA0 and DMA1 Transfers              | 1040 H          |

| Reserved                                              | 1038 – 103C H   |

| Reserved (Bits 2 – 31)  DMA In Status (B              |                 |

| Reserved                                              | 1020 – 1030 H   |

| DMA1 Control                                          | 101C H          |

| DMA1 Data Transfer Size                               | 1018 H          |

| DMA1 Address of Contiguous Host Memory – High 32 bits | 1014 H          |

| DMA1 Address of Contiguous Host Memory – Low 32 bits  | 1010 H          |

| DMA0 Control                                          | 100C H          |

| DMA0 Data Transfer Size                               | 1008 H          |

| DMA0 Address of Contiguous Host Memory – High 32 bits | 1004 H          |

| DMA0 Address of Contiguous Host Memory – Low 32 bits  | 1000 H          |

#### 2.7.1 DMA0 Address of Contiguous Host Memory (Low and High) Address: 1000 (H) (Low)

1004 (H) (High)

Length 64 bits

The start address of the Contiguous Host Memory must be written to this register by the user. The address stored in this register is automatically incremented during the process of the DMA transfer. The current value in this register is the address following (the address of) the last requested data. Upon successful completion of a transfer, this register contains the following value: Start Address + Write Transfer Size, where Start Address is the start address of the Contiguous Host Memory.

page 2 - 18 Excalibur Systems

#### 2.7.2 DMA0 Data Transfer Size

This register contains the total amount of data (in bytes) to be written during a DMA write transfer. The total transfer size must be written to this register by the user. The transfer size value stored in this register is automatically decremented during the process of the DMA transfer. The current value stored indicates the remaining amount of data that needs to be transferred. Upon successful completion of a DMA write transfer, the value of this register should be 0.

#### 2.7.3 DMA0 Control Register

Length 32 bits

Address:

Address: Length 1008 (H)

100C (H)

32 bits

This register contains information about, and controls, the DMA write data transfer.

| Bit   | Description         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-13 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 08-11 | DMA channel state   | These bits describe the state of the DMA write channel.  0000 = (idle state) Last transfer ended successfully  0001 = (idle state) Last transfer was stopped by a module  0010 = (idle state) Last transfer ended because of CPL timeout  0011 = (idle state) Last transfer ended because of CPL UR error  0100 = (idle state) Last transfer ended because of CPL CA error  0101 - 0111 = (idle state) Reserved  1000 = (busy state) The DMA channel is busy processing  1001 = (busy state) Requesting transfer. The DMA channel is in the  process of requesting data from the host computer  1010 = (busy state) The DMA channel is waiting for completion of a  read data transfer in response to a DMA read request  1011 = (busy state) Waiting for board to provide/accept data. The  DMA channel is waiting for completion of a data transfer to or from  the internal module memory.  1100 - 1111 = (busy state) Reserved |

| 04-07 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 03    | Abort DMA transfer  | 1 = Abort transfer<br>0 = no effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 02    | Start DMA transfer  | 1 = Start DMA transfer<br>0 = no effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 00-01 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

Table 2-16 DMA0 Control Register

## 2.7.4 DMA1 Address of Contiguous Host Memory

1010 (H) (Low) 1014 (H) (High)

10 14 (11) (111g

Length 64 bits

Address:

The start address of the Contiguous Host Memory must be written to this register by the user. The address stored in this register is automatically incremented during the process of the DMA transfer. The current value in this register is the address following (the address of) the last requested data.

> Upon successful completion of a transfer, this register contains the following value: Start Address + Read Transfer Size, where Start Address is the start address of the Contiguous Host Memory.

#### 2.7.5 **DMA1 Data Transfer Size**

Address: 1018 (H) Length 32 bits

This register contains the total amount of data (in bytes) to be read during a DMA read transfer. The total transfer size must be written to this register by the user. The transfer size value stored in this register is automatically decremented during the process of the DMA transfer. The current value stored indicates the remaining amount of data that needs to be transferred. Upon successful completion of a DMA read transfer, the value of this register should be 0.

#### 2.7.6 **DMA1 Control Register**

101C (H) Length 32 bits

Address:

This register contains information about, and controls, the DMA read data transfer.

| Bit   | Description         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 12-13 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 08-11 | DMA channel state   | These bits describe the state of the DMA read channel. 0000 = (idle state) Last transfer ended successfully 0001 = (idle state) Last transfer was stopped by a module 0010 = (idle state) Last transfer ended because of CPL timeout 0011 = (idle state) Last transfer ended because of CPL UR error 0100 = (idle state) Last transfer ended because of CPL CA error 0101 – 0111 = (idle state) Reserved 1000 = (busy state) The DMA channel is busy processing 1001 = (busy state) Requesting transfer. The DMA channel is in the process of requesting data from the host computer 1010 = (busy state) The DMA channel is waiting for completion of a read data transfer in response to a DMA read request 1011 = (busy state) Waiting for board to provide/accept data. The DMA channel is waiting for completion of a data transfer to or from the internal module memory. |

| 04-07 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 03    | Abort DMA transfer  | 1 = Abort transfer<br>0 = no effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 02    | Start DMA transfer  | 1 = Start DMA transfer<br>0 = no effect                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 00-01 | Reserved – set to 0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

Table 2-17 DMA1 Control Register

page 2 - 20 Excalibur Systems

#### 2.7.7 DMA Interrupt Status Register

Address: 1034 (H) Length 2 bits

Bit 0 of this register is set upon completion of a DMA transfer on DMA0 (DMA write). Bit 1 is set upon completion of a DMA transfer on DMA1 (DMA read). To clear either bit, write a 1 to the corresponding location.

**Note:** The two bits of the DMA Interrupt Status Register work together with the five bits of the Global Interrupt Status Register. When any of these seven bits are set, an interrupt is generated. To locate the source of an interrupt to the host, both of these registers need to be read.

In order to reset an interrupt, you must reset the appropriate bits of **both** the DMA Interrupt Status Register **and** the Global Interrupt Reset Register. See **2.5.3** Interrupt Status Register on page 2-13.

#### 2.7.8 Base Address for DMA0 and DMA1 Transfers

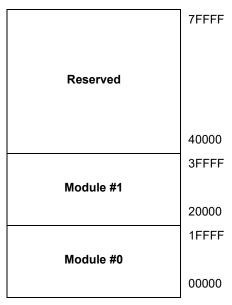

Address: 1040 (H) Length 32 bits